数字信号有两种主要形式:数字数据和数字时钟(CLK)。数字信号是当前数字电子产品中的主要信号形式,通常为单端信号,CMOS或TTL电平。我们观察到的数字信号一般是一串宽度不同的脉冲,时钟信号通常是具有相同脉宽的矩形脉冲。数字信号和CLK信号的频谱成份包含有高次谐波,信号本身及其谐波共同在电子系统内部和系统之间产生了电磁干扰(EMI)。降低EMI的一条简单、有效途径是使CLK频率产生抖动。

扩频时钟是一种减少数字芯片电磁干扰的有效方法,它采用预设好的调制波形,在一定频率范围内对时钟信号进行频率调制。扩频时钟发生器即产生扩频时钟的发生器。

背景在当今的高速数据传输系统中,串行链路结构己经成为主流.随着接口数据率的不断提高,内部的时钟频率也达到了几个G赫兹,这将使电磁干扰(Electromagnetic Interference,EMI)变得十分严重。许多消费电子产品的标准,都严格规定了电磁辐射的水平,现在有多种技术可以降低电磁干扰。常见的几种技术包括屏蔽、脉冲整形、摆率控制和扩频时钟。其中,扩频时钟(Spread-spectrum Clocking,SSC)是最适用于高速系统的性能最好、成本最低的技术。

类似于频率调制,扩频时钟技术轻微抖动系统的时钟频率使频谱扩展到一定宽度的频带上。实际上,扩频时钟没有减少各次谐波的总能量,它只是把原来非常集中的能量均匀分散到一定宽度的频带上。扩频时钟产生器(Spread-spectrum Clock Generator,SSCG)有多种实现方式,大部分是基于锁相环(Phase-lockedLoop,PLL)1。

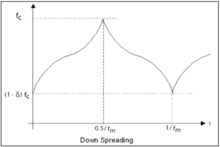

相关参数定义为了考察抖动时钟的扩展频谱,我们定义了以下扩频CLK参数:扩展率、扩频类型、调制率和调制波形。扩展率是频率抖动(或扩展)范围与原CLK频率(fC)的比值。扩频类型指向下扩频、中心扩频或向上扩频。假设扩频范围为Δf,则扩展率δ定义为:

向下扩频:δ = -Δf /fC x 100%

中心扩频:δ = ±1/2Δf/fC x 100%

向上扩频:δ = Δf/fC x 100%

调制率fm,用于确定CLK频率扩展周期率,在该周期内CLK频率变化Δf 并返回到初始频率。调制波形代表CLK频率随时间的变化曲线,通常为锯齿波。图1给出了调制波形及其与δ和fm的关系式。

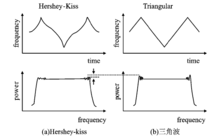

为了得到平坦的CLK频谱,一种称为“Hershey Kiss™”的特殊曲线被用作调制波形(图2)。

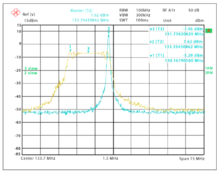

利用图1或图2所示波形扩展后的时钟在扩频范围内具有平坦的功率谱密度。图3所示曲线是MAX9492经过扩频和未经扩频情况下的时钟频谱。扩频情况下,扩展率δ为-2.5%―向下扩频;调制率fm为30kHz,CLK标称频率fC为133.33MHz。该频谱曲线是采用Rohde & Schwarz频谱分析仪测试得到的,其中分辨率带宽为100kHz,扫描频率为10Hz。从测试结果可以看出:频谱峰值降低了大约13dB,与fC谐波的衰减量相同。这说明扩频后的CLK能够在频谱峰值处提供13dB的EMI抑制2。

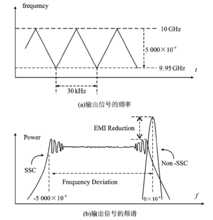

下图为扩频时钟的频率和频谱的示意图。图(a)表明扩频后输出信号的频率为三角波,三角波调制的频率为30 kHz,图(b)分别表示扩频和不扩频的频谱图。扩频之后能量不是集中在某个频点,而是均匀分布在一定宽度的频带上。

峰值降落是一个非常关键的指标,它指的是未扩频的时钟信号的幅度与扩频后的信号幅度的比值,用符号 表示。为了降低系统时钟的电磁干扰对周围电路的影响,我们希望

表示。为了降低系统时钟的电磁干扰对周围电路的影响,我们希望 越大越好。峰值降落和以下因素有关:调制频率fm,时钟的频率偏差,调制波形和时钟基频

越大越好。峰值降落和以下因素有关:调制频率fm,时钟的频率偏差,调制波形和时钟基频 。其中最关键的因素是调制波形的选择与产生。

。其中最关键的因素是调制波形的选择与产生。

当调制频率低于频谱分析仪的分辨带宽(Resolution Bandwidth, RBW)时,最优的调制波形是一种称为"Hershey kiss"的非线性曲线。而且,当调制频率接近分辨带宽时,峰值降落会进一步增大。如下图(a)所示,当采用Hershey-Kiss调制时,信号能量均匀地分布在一定频带上,扩频效果很好,图2(b)是三角波调制,此时频带两端有一些峰值,无法达到最大的峰值降落.Hershey kiss曲线的实现比较复杂,需要查找表、SRAM或者 调制器,带来较大的面积和功耗。相比之下,三角波调制波形用计数器就能实现,非常简单。不过三角波在峰值降落上,没有“Hershey kiss"调制波形效率高。为了降低功耗和面积,采用三角波调制。

调制器,带来较大的面积和功耗。相比之下,三角波调制波形用计数器就能实现,非常简单。不过三角波在峰值降落上,没有“Hershey kiss"调制波形效率高。为了降低功耗和面积,采用三角波调制。

扫码下载APP

扫码下载APP

科普中国APP

科普中国APP

科普中国

科普中国

科普中国

科普中国